ICC_workshop的最后一个实验了。在这次的实验中,由于我使用ICC的版本与workshop的lab不是同一个版本,因此在后面的实验过程不是很顺利,主要是在LVS的过程中,最后的LVS没有通过。但是还是在这里说一下流程吧,在这个实验中,主要完成下面的事情:

·DRC和LVS检查

·进行连线扩展和加宽连线来减少关键面积

·使用二极管修复天线违规

·使用填充单元填充核心中未填满的位置

·进行冗余通孔插入(冗余通孔的插入是可选的)

·填充金属以满足金属密度要求

·生成GDSII数据

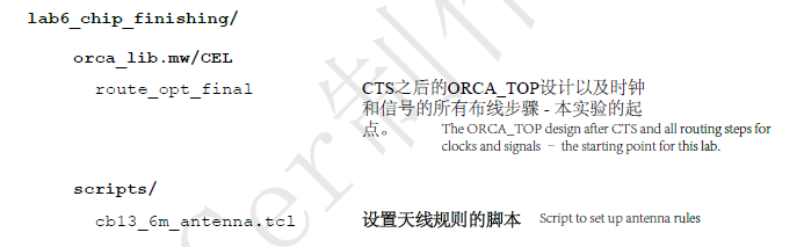

首先需要准备下面的数据:

然后就可以开始试验了:

·加载和分析设计

--->记载库和设计

--->验证是否有DRC和LVS违规:

verify_zrt_route

verify_lvs

--->有,则进行修复(具体怎么修复这里不进行介绍,我也不知道具体的细节,但是是有这个流程的)

--->查看是否有违规:

--->有,则进行修复:psynopt -xxx

·减少关键面积

--->通过GUI查看关键面积(short critical area)

--->查看、保存修改前短路的关键面积的报告:

report_critical_area -fault_type short

sh mv output_heatmap cca.short.before.rpt

--->进行连线扩展,减少短路的关键面积:

spread_zrt_wires

--->查看、保存连线扩展后的关键面积报告:

report_critical_area -fault_type short

sh mv output_heatmap cca.short.after.rpt

--->查看、保存修改前开路的关键面积的报告:

report_critical_area -fault_type open

sh mv output_heatmap cca.open.before.rpt

--->进行加宽导线,来减少开路的关键面积:

widen_zrt_wires

--->查看、保存加宽导线后的关键面积报告:

report_critical_area -fault_type open

sh mv output_heatmap cca.open.after.rpt

--->查看是否有DRC、LVS以及时序等违规:

verify_zrt_route

verify_lvs

rc

--->如果有,则进行修复(具体怎么修复这里不进行介绍,我也不知道具体的细节,但是是有这个流程的),修复后保存设计:save_mw_cel -as chip_finish_ca

·使用二极管修复天线违规

--->安装一组天线规则:

source -echo scripts/cb13_6m_antenna.tcl

天线规则设置确定如何处理金属层的模式

--->检查已定义的当前天线比率规则,并检查您的设计中是否存在任何接触违规:

report_antenna_rules

verify_zrt_route

--->进行天线违规修复:

set_route_zrt_detail_options -insert_diodes_during_routing true

route_zrt_detail -incremental true

--->检查lvs违规:

verify_lvs

--->如果有lvs错误,则重新定义P/G环,看是否由插入二极管引起:

derive_pg_connection -power_net VDD -power_pin VDD -ground_net VSS -ground_pin VSS

derive_pg_connection -power_net VDD -ground_net VSS -tie

--->再检查各种违规:

verify_zrt_route

verify_lvs

rc

如果有违规,这时候的违规就不是天线违规引起的了,通过其他手段进行修复

--->保存设计:save_mw_cel -as chip_finish_antenna

·插入标准填充单元

--->插入标准单元:

insert_stdcell_filler -cell_with_metal "feedth9 feedth3" -connect_to_power VDD -connect_to_ground VSS -between_std_cells_only

--->插入非金属填充单元:

insert_stdcell_filler -cell_without_metal "feedth" -connect_to_power VDD -connect_to_ground VSS -between_std_cells_only

--->查看是否有违规(一般没有):

verify_zrt_route

verify_lvs

rc

·插入冗余过孔

--->成物理设计报告以确定现有的双重过孔率:

report_design_physical -route

--->生成 将在冗余过孔插入期间 自动使用的 过孔映射表:

insert_zrt_redundant_vias -list_only

--->使用默认的中等强度进行插入冗余过孔:

insert_zrt_redundant_vias -effort medium

--->检查是否有违例:

verify_zrt_route

verify_lvs

rc

--->插入金属,以满足金属密度要求:

insert_metal_filler -routing_space 2 -timing_driven

--->确保在本阶段添加的单元和所有电源地的pin都连接到电源的网络:

derive_pg_connection -power_net VDD -power_pin VDD -ground_net VSS -ground_pin VSS

derive_pg_connection -power_net VDD -ground_net VSS -tie

--->检查是否违规:

verify_zrt_route

verify_lvs

rc

---->保存设计,写出GDSII文件:

save_mw_cel -as chip_finish_final

close_mw_cel write_stream -cells chip_finish_final orca.gdsii close_mw_lib